기술 개요

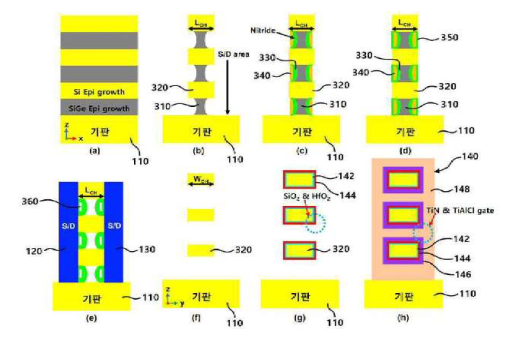

- 나노시트(Nanosheet) FET(field-effect transistor) 소자 및 제조 방법에 관한 것

기존기술 한계

- 나노시트 FET(Nanosheet FET)는 게이트(gate)가 채널(channel)의 전면을 둘러싸고 있는 둥근 나노와이어(nanowire) 형태를 가짐.

- GAA(gate-all-around) FET 보다 더 진보된 형태의 소자 구조로서, 채널을 여러 개의 다리 형태로 구현한 MBC(Multibridge-Channel) FET가 대표적.

- 나노시트 FET는 채널의 구조가 원형이 아닌 직사각형의 나노시트 형태로 제작되어, 게이트와 채널이 접하는 면적 및 출력성능을 극대화 가능.

- 그러나 나노시트 FET에서의 게이트 절연막(SiO2 및 high-kdielectric)은 결함이 발생하기 쉬워 소자의 신뢰성에 문제가 우려됨.

개발기술 특성

- 게이트 전극과 게이트 전극 사이에 의도적으로 전류를 인가하여, 발생하는 열을 활용하여 소자를 자가 치유할 수 있는 나노시트 FET 제조 방법 제공

- 3개의 채널을 포함하는 나노시트 FET 소자에 대해 전류 어닐링 공정을 수행함으로써, 소자의 수명 연장이 가능하고 신뢰성을 개선할 수 있는 효과 존재.

- 나노시트 FET 소자에서 내부가 진공 상태인 이너 스페이서 구조를 제안함으로써, 전류 어닐링 과정에서 발생하는 전력 소모를 감소시킬 수 있는 효과 존재.

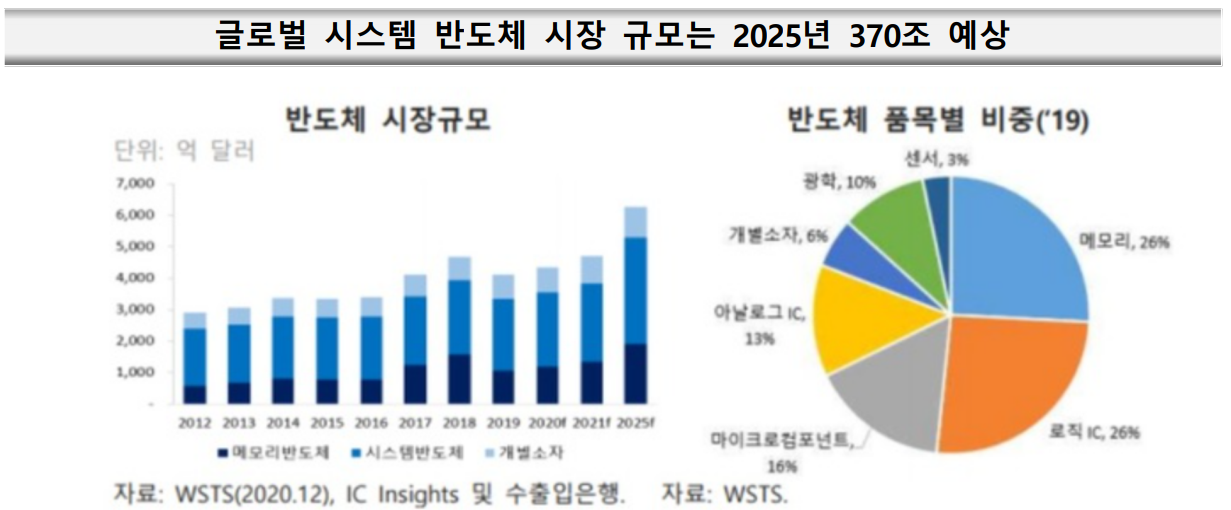

시장동향

- 글로벌 반도체 시장은 PC/모바일 등 IT 기기 발달과 함께 시장규모도 지속 확대됨.

- 최근 4차 산업혁명의 본격화로 AIㆍIoTㆍ자율주행차 등의 발달로 시장규모도 확대되고 있음

기술동향

- 반도체는 4차 산업 혁명의 모든 분야에 필수적으로 활용되는 미래 기술의 핵심

- 반도체 기술 발전은 인공지능의 성능 향상을 견인하고, 인공지능의 가능성에 대한 발견으로 많은 반도체 기업들이 인공지능 산업에 참여하고 있음